# FPGAによる仮想レオロジー物体の リアルタイム変形計算

立命館大学ロボティクス学科 友國誠至,平井慎一

# Real-time Computation of Rheological Deformation Using FPGA

Seiji TOMOKUNI and Shinichi HIRAI Department of Robotics, Ritsumeikan University

Abstract:Deformable soft objects such as food and tissue show both elastic and viscoplastic properties, and are referred to as rheological objects. We designed an computational hardware using an FPGA(Field Programmable Gate Array) and realized a system that computes the rheological deformation 18 times as fast as a PC with a Pentium IV 1.7 GHz. Our estimations show that an FPGA can compute the deformation 243 times faster than the PC.

## 1 はじめに

近年,医療分野やエンターテイメント分野において,リアルタイムでの物理シミュレーションが一般的なものとなりつつある.しかし,多くの場合,ハードウェアの計算能力が十分ではなく,特に力覚提示を伴う場合には1000Hz程度のリフレッシュレートが必要となるため,複雑な物体の変形計算に難がある状況である.

一方で,八ードウェアの分野では,FPGAと呼ばれる回路の組み換えが可能なLSIが登場し,急激にその回路規模を増している.FPGAでは各演算回路が同時並行的に動作するため,シミュレーション分野によく見られる並列計算アルゴリズムとの親和性が高く,シミュレーションの高速化に一定の効果を発揮する.今回,我々はFPGA上に演算回路を実装し,PentiumIV1.7GHz 搭載 PC の 18 倍の速度での仮想レオロジー物体の変形計算を実現した.また,現行の FPGA を用いて同 PC の 243 倍の速度での計算が可能であるという試算を得た.

# 2 レオロジー物体のモデル

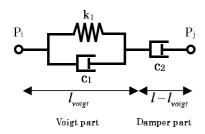

レオロジー物体とは、食品や生体組織、粘土などに代表される柔軟物であり、完全弾性物体と塑性物体の中間的な性質を有する物体である.レオロジー的性質を表現する一次元モデルとしては  ${

m Fig.1}$  に示す三要素モデル  ${

m [1]}$  があり、フォークトモデルと単一のダンパを直列に接続したものである.三要素モデルの長さおよび三要素モデルのフォークト部の長さをそれぞれ l,  $l_{voigt}$  とし,フォークト部の弾性係数および粘性係数を  $k_1,c_1$ ,ダンパ部の粘性係数を  $c_2$  として,定数  $A=-k_1/(c_1+c_2)$ ,定数  $B=c_2/(c_1+c_2)$  とおくと,フォークト部の比率の変化および三要素モデル

Fig. 1: Three element model

の発生する力は,

$$\dot{l}_{voiat} = A \left( l_{voiat} - L \right) + B\dot{l} \tag{1}$$

$$f = -c_2(\dot{l} - \dot{l}_{voiqt}) \tag{2}$$

で表される.

三要素モデルの両端には質点  $P_i$ ,  $P_j$  が繋がっており,物体の変形は三要素モデルから各質点に加わる合力による運動方程式に基づいて計算される.物体は三角形要素あるいは四面体要素を組み合わせて表現し,各要素の頂点に質点を配し、頂点間を結ぶ稜線を三要素モデルとする.

#### 3 レオロジー変形処理回路の概要

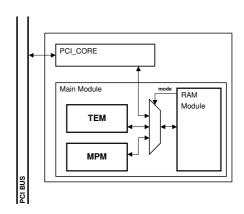

本研究で設計した変形計算回路の概要を Fig.2 に示す.

Fig. 2: Schematic computation module

図中において TEM は各稜線に配置された三要素モデルによって生じる力および三要素モデルフォークト部の変形を計算する回路であり (1),(2) 式の演算を行う.MPMは一般的な運動方程式に基づく質点の運動を計算する回路である.それぞれの回路はオイラー法の演算を含むパイプライン回路となっており,この二つの回路が交互に動作することで,1ループ分のシミュレーションが行われる.

本研究では FPGA として Xilinx 社の VirtexII XC2V6000 を用い, PCI バスを介して XC2V6000 搭載ボードを PC と接続する. 回路は PCI バスのクロックと同期し, 周波数 33MHz で動作させる. また変数の値は8bit 目を小数点位置とする 16bit 固定小数点で表現する.

Table 1: Size of Circuits

|             | flip-flops | slices | multipliers |

|-------------|------------|--------|-------------|

| All modules | 8,720      | 6,875  | 25          |

| TEM         | 6,880      | 4,144  | 16          |

| MPM         | 1045       | 640    | 9           |

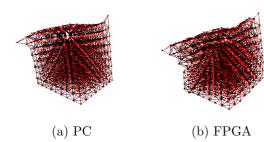

Fig. 3: Deformed shape of rheological objects

Table 2: Computational time

|                      | time[ms] |

|----------------------|----------|

| PC(PentiumIV 1.7GHz) | 3.65     |

| FPGA(XC2V6000)       | 0.20     |

固定小数点による誤差を減少させるため,四捨五入丸めを導入し,また静的に小数点位置を設定できる定数値の固定小数点位置を最適な値に設定し,局所的に小数点位置を変更することで回路規模の増大を抑えつつ,定数値の精度の向上を行った.設計した回路の回路規模を Table1 に示す.今回設計した回路は,XC2V6000 の使用可能 slice 数の 20 %を占めている.

#### 4 動作結果

PC と FPGA で  $9\times 9\times 9$  の質点を持つ仮想レオロジー物体の上部二箇所に外力を加えた場合の変形を計算し,結果を比較した.得られた変形形状を Fig.3 に示す.また,PC と FPGA のそれぞれで計算に要した時間を,Table2 に載せる.表より,FPGA が PC の 18.25 倍の計算速度を実現していることが分かる.FPGA の計算精度は PC より低く,物体の変形形状は異なるが,定性的には類似した形状が得られた.

## 5 実現可能な処理速度の試算

今回の回路には TEM と MPM を一つずつ実装した.しかし,質点を複数のグループに分けることで複数回路による並列計算も可能であり,その処理能力は試算から得られる.回路 TEM が一回のループに要するクロック数は,

$$c_{te} = \frac{n_{es} + 2n_{et}}{P_{te}} + d_{te} \tag{3}$$

である  $.n_{es}$  ,  $n_{et}$  ,  $P_{te}$  ,  $d_{te}$  はそれぞれ , 同一のグループ間を接続するエッジの総数, 二つのグループにまたがるエッジの総数, TEM の回路数, TEM のパイプライン段数である. 回路 MPM が一回のループに要するクロック

(A) PC  $(5 \times 6 \times 6)$  (B) FPGA  $(15 \times 15 \times 16)$

Fig. 4: Maximum feasible virtual object size

数は,

$$c_{mm} = \frac{n_m}{P_{mm}} + d_{mm} \tag{4}$$

である.ここで, $n_m$   $P_{mm}$ , $d_{mm}$  はそれぞれ質点の総数,MPM の回路数,MPM のパイプライン段数である.これらより,1 ループ当りの処理時間は,

$$t_s = \frac{c_{te} + c_{mm}}{r_c} \tag{5}$$

となる.ここで, $r_c$  は FPGA に与えるクロック周波数である.今回の回路では,XC2V6000 の RAM 容量の制約から格納可能な物体規模が最大  $15 \times 15 \times 16$  の質点を持つ物体までに限られるが,そのサイズの物体の処理に要する時間は,0.712ms である.したがって,1000Hz の更新頻度を必要とする力学提示用途では,PC と FPGA で扱える物体の規模はそれぞれ Fig.4 に示すものとなる.

今回は PCI バスと同期して  $33 \rm{Mhz}$  で回路を駆動したが,VirtexII 内蔵回路による逓倍で  $66 \rm{MHz}$  駆動を行うことが可能であり,また  $\rm{XC2V6000}$  には, $\rm{TEM}$  と  $\rm{MPM}$  をそれぞれ4つずつ実装する余裕がある.これらを実装すると  $15 \times 15 \times 16$  の物体の計算に必要な時間は  $0.0955 \rm{ms}$  となり,PC で同サイズの物体を計算した場合の処理時間の実測値  $23.2 \rm{ms}$  に対し, $\rm{FPGA}$  は 243 倍の速度で計算を行えることが試算より得られた.

#### 6 おわりに

レオロジー変形計算回路を実際に動作させ,レオロジー変形計算の高速化を実現するとともに,試算から現行のFPGAで実現可能な計算速度を示した.今後の課題としては,力覚提示デバイスとの連携,体積効果および位相保持[1]の実装が考えられる.

FPGA は並列アルゴリズム全般に利用することができ、他のシミュレーション分野においても今後の発展が期待される.

#### 参考文献

[1] 友國誠至,杉山勇太,平井慎一,"実時間計算可能な 仮想レオロジー物体の構築",日本バーチャルリアリティ学会論文誌,Vol.8,No.3,pp.247-254,2003.