# CMOS + FPGA Vision を用いた Matched filter の高速化

清水一弘(立命館大学) 平井慎一(立命館大学)

# Parallel matched filter implemented on CMOS + FPGA Vision

\*Kazuhiro SHIMIZU (Ritsumeikan Univ), Shinichi HIRAI (Ritsumeikan Univ)

**Abstract**— In this paper, we describe a parallel matched filter implemented on a CMOS + FPGA Vision. This algorithm can detect robustry the position of a planar motion object, but requires much computation time for 2D-FFT. Its implementation on an FPGA is expected to reduce the computation time. This paper shows the logic circuit to perform matched filter.

### 1. はじめに

ロボット制御における視覚センサの利点は,非接触 で観測対象の位置・姿勢を認識できることである.そ の利点を活かし,視覚センサをロボット制御へ応用す る研究が盛んに行われている.石川らは,画素ごとに センサと処理要素を並列にならべたアーキテクチャを 提案し,フィードバックレート 1000Hz を有するビジョ ンシステムを開発している[1].しかし,処理要素を並 列に配置しているため,画像重心やフィルタ処理など の局所演算は高速に演算できるが,ハフ変換やフーリ 工変換などのグローバル演算の実装は困難である.石 井らは,撮影されたメガピクセルの画像領域から特定 の画素を知的選択し処理する Mm Vision を提案して いる[2].1フレームの画像に対して計測する画像領域 を限定することにより, PCI バスの通信速度のボトル ネックを解消し高リアルタイム性を実現している. し かしこの手法では,検出対象に対してオクルージョン が生じた場合、リアルタイム性を確保できなくなると いう問題点がある.そこで我々は,1000Hz で撮影さ れた高解像度の画像全域を処理する CMOS + FPGA Vision を提案している. 画像重心計算アルゴリズムを CMOS + FPGA Vision に実装し, 1280x504pixelの 画像から LED の位置を 1ms 以内で検出することに成 功した [3]. 次に,グローバル演算を含むアルゴリズ ム Matched filter の CMOS + FPGA Vision 実装を 目指している [4][5] . 画像サイズ 64x64pixel において , Matched filter を CMOS + FPGA Vision に実装し, 円形マーカを用いた実験を行った.その結果,輝度の変 化,欠け,背景下においてでもロバストであることが確 認できた [6]. 本論文では,画像サイズを 256x266pixel に拡大し,各演算回路のシミュレーションを行った.そ の結果を報告する.

# 2. ビジョンアルゴリズム

### 2.1 Matched Filter

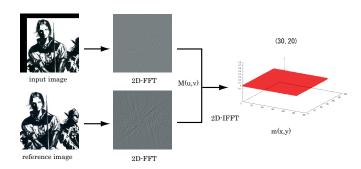

Matched filter は,テンプレート画像と入力画像の 2次元フーリエ変換から得られるスペクトルを用いて相関を求める手法である.このアルゴリズムの特徴は,入力画像の輝度の変化や対象物の欠けに対してロバストに検出できることにある.テンプレート画像を  $f_{ref}(x,y)$ ,

入力画像を  $g_{inp}(x,y)$  とし,これらの 2 次元離散フーリエ変換をそれぞれ  $F_{ref}(u,v)$ , $G_{ref}(u,v)$  とする.このとき相関関数 m(x,y) は,次式で定義される M(u,v)を 2 次元逆離散フーリエ変換することにより得られる.

$$M(u,v) = \frac{G_{inp}(u,v)}{F_{ref}(u,v)} \tag{1}$$

(1) 式で定義された相関関数は,そのピークの座標から画像の 2 次元の移動量の検出が可能であり,その相関値から入力画像の類似度をはかることができる.Fig.1 は,テンプレート画像と入力画像から Matched filter を計算した結果である.入力画像は,テンプレート画像に対して (x,y)=(30,20) 移動している.これらの相関関数は,2 つの画像の移動量に対応した座標 (x,y)=(30,20) で最大値をとることが分かる.

Fig.1 Matched filter

# 3. CMOS + FPGA Vision

### 3.1 コンセプト

${

m CMOS} + {

m FPGA}$   ${

m Vision}$  は, $1000{

m Hz}$  で撮影可能な  ${

m CMOS}$  センサと画像の特徴量を計算する  ${

m FPGA}$  から 構成される. ${

m CMOS}$  センサで撮影された画像は,画像 処理アルゴリズムが実装されている  ${

m FPGA}$  に転送される. ${

m FPGA}$  上に構築された画像処理回路は,撮影された画像から対象とする画像の特徴量を計算する.算出 された演算結果は, ${

m PCI}$  バスを経由して  ${

m PC}$  へ転送される.

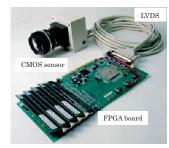

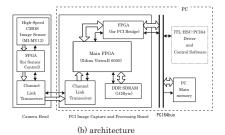

## 3.2 システム構成

CMOS + FPGA Vision は,画像技研製 ITL-HSC-AD-SDK を使用している . Fig.2(a) に示すように CMOS + FPGA Vision は, CMOS センサ, FPGA と LVDS から構成されている. CMOS センサは, Micron Imaging 社製 MI-MV13 を使用し, 1280 × 504pixelの 画像を 1000fps で撮影できる . FPGA ボードは , Xilinx 社製 Virtex-ll の FPGA が搭載されており,600 万シス テムゲート相当の論理回路を構築できる. Fig.2(b) に CMOS + FPGA Vision のシステム構成を示す . CMOS センサで撮影された画像は, LVDS インターフェイス を経由して FPGA ボード上の FPGA へ転送される. FPGA には画像処理アルゴリズムが実装されており, CMOS センサの画像のキャプチャーと同期しながら画 像処理を行う.その画像処理の演算結果のみを PCI バ スを介して PC と通信する . FPGA 内の画像処理回路 は,外部の DDR-SDRAM と接続しており必要に応じ てデータを保存できる.

(a) appearance

Fig.2 CMOS + FPGA Vision

# 4. シミュレーション

本研究において Matched filter の回路設計には,ハードウェア記述言語である Xilinx 社製 ISE 8.2 Foundation の Verilog-HDL を,シミュレーションには, Mentor Graphics 社製の ModelSim SE を使用した.表1 に Matched filter のシミュレーション結果を示す. Matched filter の最大駆動周波数は67.7MHz と判明した.本研究では,66MHzで動作させる.

# 5. おわりに

本稿では,Matched filter の回路設計につて報告した. 画像サイズ  $256 \times 256$  pixel において Matched filter の計算時間は,PC で 161ms である.CMOS + FPGA Vision では 5ms 以内で処理が完了する.今後の展開として,マーカを用いた実験を行いロバスト性を確認する.

Table 1 Consumed FPGA resorces in matched filter

### 2D-FFT

| Logic Utilization | Used  | Available | Utilization |

|-------------------|-------|-----------|-------------|

| Slices            | 5,412 | 33,792    | 16%         |

| Block RAMs        | 2     | 144       | 1%          |

| MULT18X18s        | 36    | 144       | 25%         |

### complex quotient

| Logic Utilization | Used  | Available | Utilization |

|-------------------|-------|-----------|-------------|

| Slices            | 4,884 | 33,792    | 14%         |

| MULT18X18s        | 6     | 144       | 4%          |

### 2D-IFFT

| Logic Utilization | Used  | Available | Utilization |

|-------------------|-------|-----------|-------------|

| Slices            | 5,412 | 33,792    | 16%         |

| Block RAMs        | 2     | 144       | 1%          |

| MULT18X18s        | 36    | 144       | 25%         |

#### total

| Logic Utilization | Used   | Available | Utilization |

|-------------------|--------|-----------|-------------|

| Slices            | 18,348 | 33,792    | 54%         |

| Block RAMs        | 114    | 144       | 79%         |

| MULT18X18s        | 43     | 144       | 29%         |

### 参考文献

- [1] 石川正俊: 超高速ビジョンの展望, 日本ロボット学会誌, Vol.23, No.3, pp.2-5, 2005.

- [2] 石井抱, 杉山克彦, 加藤一樹, 黒住省吾, 沼田暁彦, 田嶋健司: 知的画素選択機能を有する高速・高空間解像度ビジョンシステム, 第5回 計測自動制御学会 システムインテグレーション部門講演会 (SI2004) 講演論文集 3A2-2, 2004.

- [3] 清水一弘 , 高橋考作 , 平井慎一 : CMOS センサと FPGA を用いた高速・高解像度ビジョンシステムの構築 , ロボティクス・メカトロニクス'05 講演会予稿集 CD-ROM, 2005.

- [4] 清水一弘, 山中雅史, 平井慎一, CMOS + FPGA Vision, ロボティクス・メカトロニクス'06 講演会予稿集 CD-ROM, 2006.

- [5] Kazuhiro Shimizu and Shinichi Hirai, CMOS+FPGA Vision System for Visual Feedback of Mechanical Systems, Proc. IEEE Int. Conf. on Robotics and Automation, pp.2060-2065, Orlando, May, 2006.

- [6] 清水一弘, 平井慎一, Matched filter の CMOS + FPGA Vision 実装, 第 23 回日本ロボット学会学術講演会予稿集 CD-ROM, 2006.